五级流水

五级流水阶段:

- 取值IF

- 指令译码 ID

- 执行部分 EX

- 访存 MEM

- 寄存器堆写回 WB

七级流水

- 将IF段划分成IFA、和IFB

- IFA 确定下一拍的指令地址PC

- IFB 从ICache中取出指令

- 将MEM瓜分成MA,和MB

- MA处理异常,确定访存地址,写内存,通知协处理器处理异常。MA段标记延迟槽。访问外存时,MA发出访存虚拟地址给MB

- MB将虚拟地址转换成物理地址并访存。处理异常,更改CPU状态寄存器

使用Monitor来控制流水线的暂停和清除

?异常处理

冲突处理

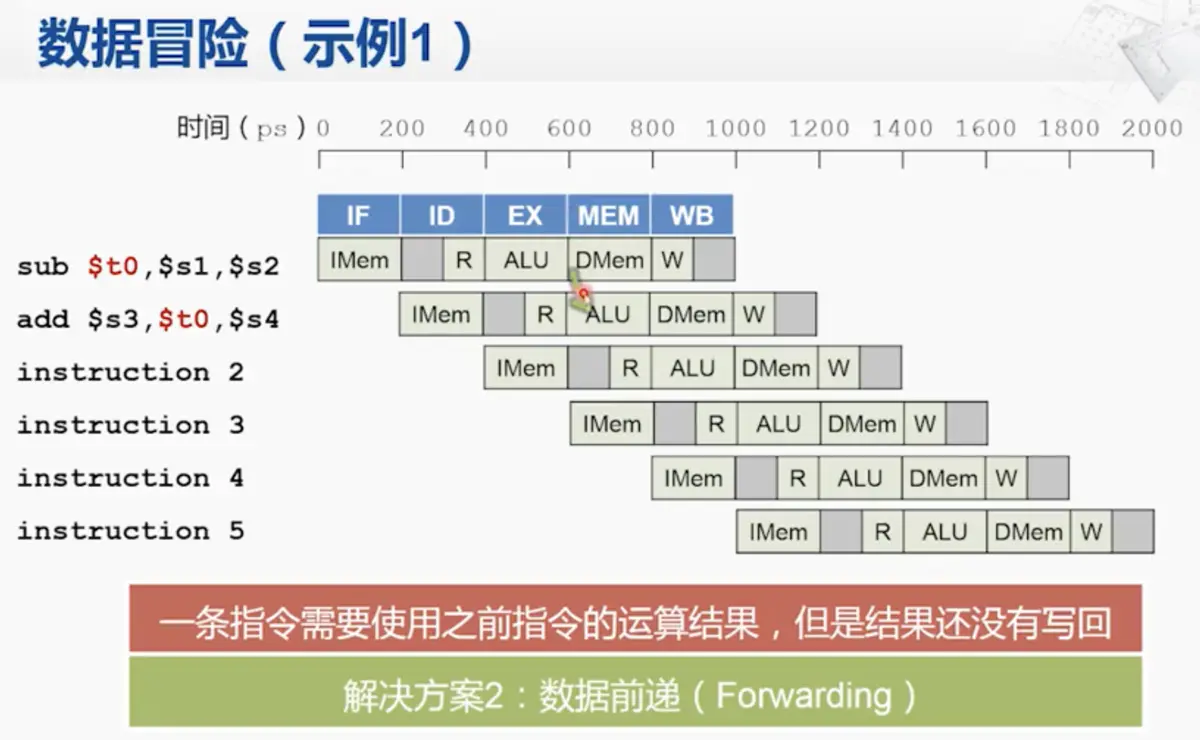

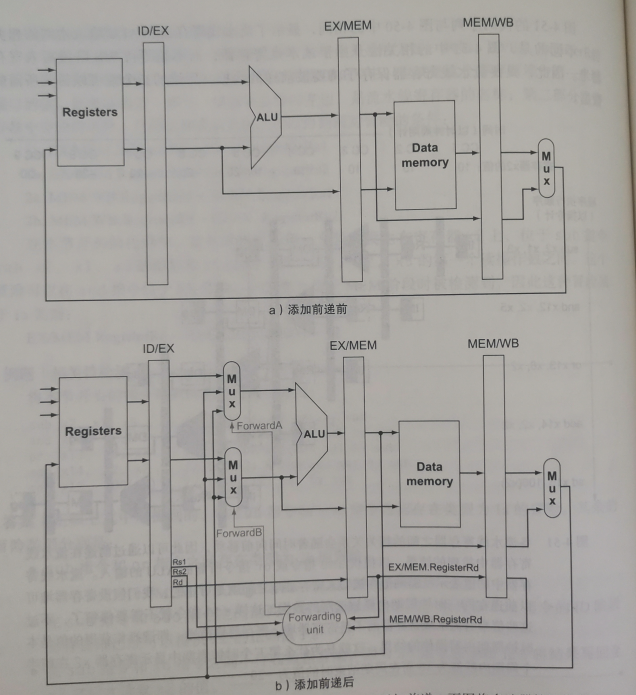

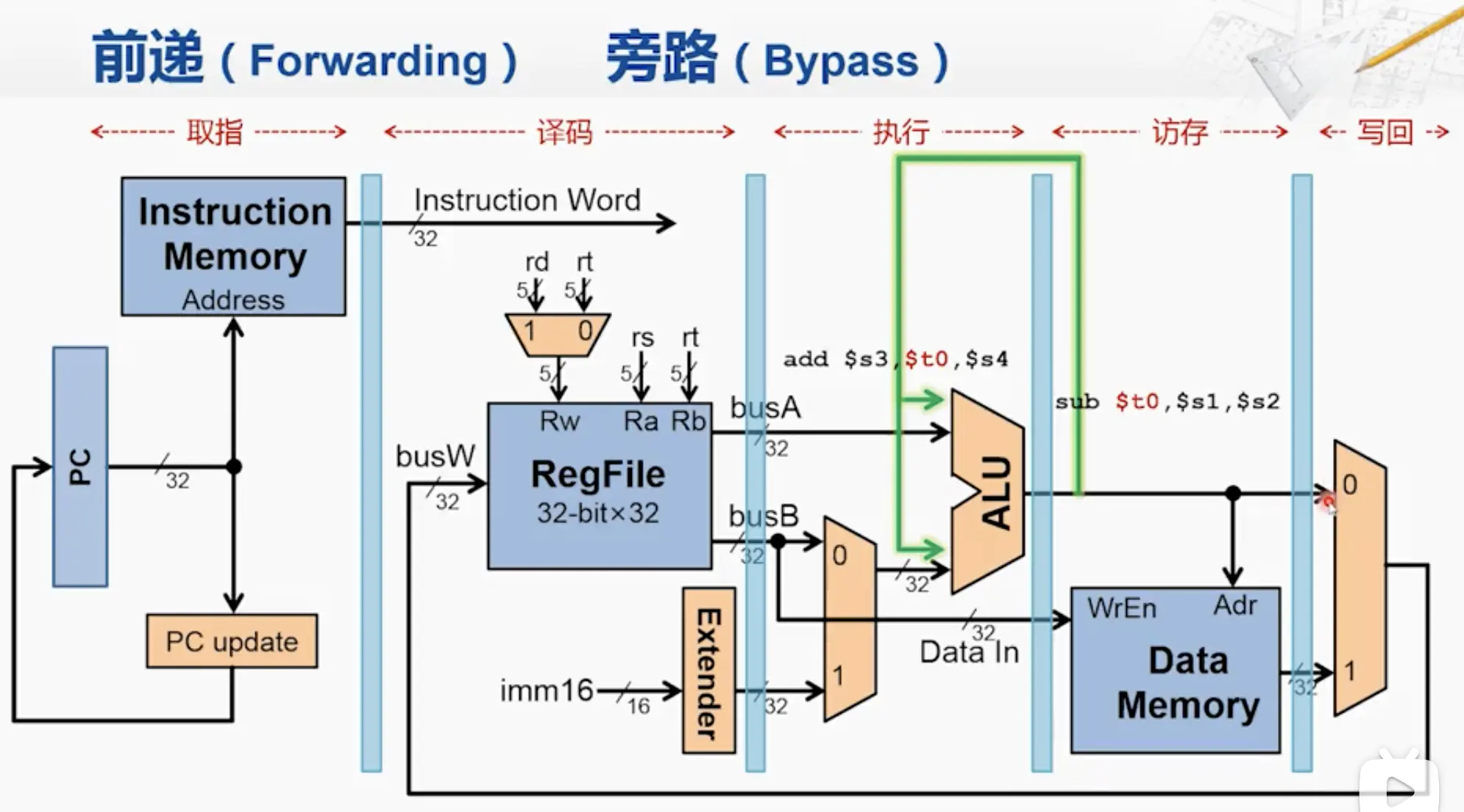

参考:数据冒险的解决

单发射仅需考虑先写后读问题,可采用数据前递和流水线暂停方式(产生bubble)来处理冲突。

数据前递更为高效:

当发生先写后读问题时,虽然前一条指令还没有写进去,但是运算结果早就已经出来了,所以这个时候可以通过旁路将结果直接传递给下一条指令

但是如果前一条指令是load,而下一条指令需要使用load的数据,那数据前递是无法处理的,这个时候可以通过插入空泡处理。